在電路設(shè)計(jì)的時(shí)候�,在一塊PCB板上存在多種電源����、多種地的情況越來越多��,例如3.3V,2.5V���,1.8V����,1.5V等電源中常見的種類����,AGND(模擬地)DGND(數(shù)字地)、PGND(保護(hù)地)等不同功能所需的地平面縱橫交錯���,一部分IC明確要求本IC要進(jìn)行單點(diǎn)接地�����,以及所需的電源���、地平面挖空。為了保證這些地���、電源都有高的可靠性�,將每一種電源��、地分配一層,即一個(gè)平面����,必然導(dǎo)致電路板疊層的增加,電路板制作的成本大幅度升高����。為了兼顧節(jié)約成本和保證電路板的可靠性,工程師在PCB設(shè)計(jì)的時(shí)候�����,會按照電路板的特點(diǎn)�����、將兩種或者幾種PCB的電源或地設(shè)計(jì)在同一個(gè)平面上���,從而導(dǎo)致了電源���、地平面的不完整,即地(電源)層分割��。

一、PCB板的跨分割設(shè)計(jì)

電路上PCB走線穿過地(電源)層分割���,信號的完整性會受到很大的影響,以及電路的EMI和EMC特性也發(fā)生變化�,這就是跨分割問題。這些也往往是電子工程師容易忽略的問題����。跨分割問題的產(chǎn)生主要有兩個(gè)來源:

1 電源/地平面的分割

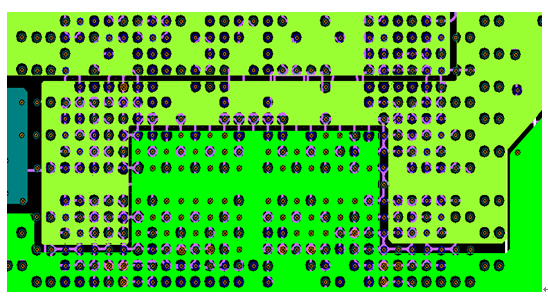

在同一層電源層上有幾種不同的電源�����。當(dāng)PCB走線穿過這個(gè)分割帶時(shí)���,跨分割問題產(chǎn)生了�,如下圖所示:

2 密集過孔或密集插裝(壓接)器件管腳定義不當(dāng)造成的分割

密集過孔或密集插裝(壓接)器件在管腳定義時(shí)如果分布得不合理�,而管腳之間的距離很小,會在地層或者定義層造成了一個(gè)狹長的隔離帶���。如果有走線穿過這個(gè)分割�����,就造成做跨分割現(xiàn)象�����。如果有走線穿過這個(gè)分割帶時(shí)��,跨分割問題也產(chǎn)生了��。這類問題主要出現(xiàn)在電路中總線布線時(shí)容易出現(xiàn)���,必須引起廣大工程師的注意���。

二、PCB板的跨分割走線的危害

跨分割走線的主要危害包括:

( 1 )導(dǎo)致走線的阻抗不連續(xù)��;

(2)容易使信號之間發(fā)生串?dāng)_�;

(3)可能引起信號的反射;

(4)增大電流環(huán)路面積�����,加大環(huán)路電感����,使輸出的波形容易振蕩;

(5)增加向空間的輻射干擾,同時(shí)易受空間磁場的影響�;

(6)加大與板上其他電路產(chǎn)生磁場耦合的可能性;

(7)環(huán)路電感上的高頻壓降構(gòu)成共模輻射源��,并通過外接電纜產(chǎn)生共模輻射

三����、PCB板避免跨分割的辦法

跨分割走線給電路帶來很大的危害����,我們在實(shí)際電路的時(shí)候,應(yīng)該盡量避免造成跨分割現(xiàn)象�,主要注意以下幾點(diǎn):

(1)走線避免穿越分割帶,走線的時(shí)候考慮地����、電源的分割,讓走線繞開電源的分割問題��,也可以增加電路的疊層數(shù)來避免跨分割問題��。

(2)通常布線的時(shí)候���,電源分割是在布信號線之后設(shè)計(jì)��,做電源或地分割時(shí)�����,一定要注意在地�����、電源分割的時(shí)候�,會對哪些信號造成影響,會造成哪些信號線的跨分割走線��,哪些是我們可以避免的����,注意適當(dāng)?shù)卣{(diào)整地、電源分割�。

(3)過孔設(shè)計(jì)和散孔不應(yīng)過于密集,造成地�����、電源平面的隔離帶�。

(4)插裝器件或者接插件在定義時(shí),要分布地合理�����,充分考慮對地、電源平面的影響����,是否造成分割,導(dǎo)致EMI增強(qiáng)��。